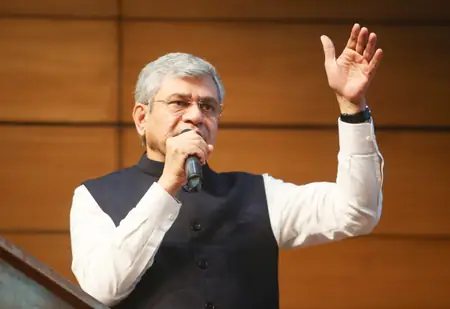

Ashwini Vaishnaw, Union Minister, spotlighted India’s swift advancement in semiconductor human capital development. The C2S initiative targets 85,000 design engineers, marking a pivotal step in national tech self-sufficiency.

Integral to ISM, this program emphasizes training and upskilling to support the emerging domestic chip industry. Substantial progress in the opening four years of the 10-year plan signals strong momentum.

World-renowned EDA platforms from Synopsys, Cadence Design Systems, Siemens, Renesas Electronics, Ansys, and AMD are now accessible in 315 academic centers. Students gain real-time expertise in chip design intricacies.

Mohali’s SCL laboratory brings designs to life through fabrication, packaging, and testing, providing end-to-end immersion for participants.

Recognized globally as the biggest open-access EDA program, it has amassed over 18.5 million hours in training. Engagement cuts across India’s geography, uniting talent from every corner.

Vaishnaw outlined explosive sector growth—from $800-900 billion to $2 trillion—spurring 2 million skilled roles worldwide. Indian youth are primed to capture a significant share.

Under ISM 2.0, outreach will extend to 500 institutions, fortifying capabilities in design, manufacturing, and beyond. This strategic escalation promises to propel India onto the world stage as a semiconductor titan.